# **Sub-1GHz RF Transmitter**

BC2102

Revision: V2.00 Date: May 07, 2024

www.holtek.com

# **Table of Contents**

| Features                                  |    |

|-------------------------------------------|----|

| Abbreviation Notes                        | 3  |

| Development Tools                         | 3  |

| General Description                       | 4  |

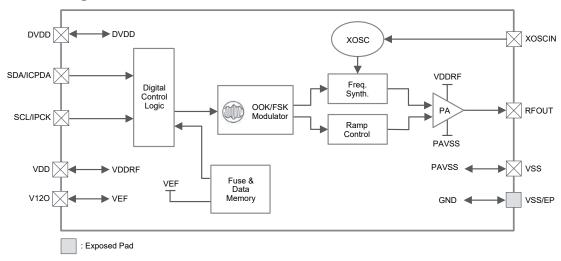

| Block Diagram                             | 4  |

| Pin Assignment                            |    |

| Pin Description                           | 5  |

| Absolute Maximum Ratings                  | 5  |

| D.C. Characteristics                      |    |

| A.C. Characteristics                      | 6  |

| RF Characteristics                        | 6  |

| I <sup>2</sup> C Characteristics          | 7  |

| Power on Reset Electrical Characteristics | 8  |

| Functional Description                    | 8  |

| Solution Overview                         |    |

| State Control                             | 9  |

| Register Map                              | 12 |

| Application Circuits                      | 16 |

| 433MHz Application Example                | 16 |

| Evaluation Board Circuit                  | 16 |

| Package Information                       | 17 |

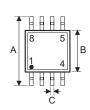

| 8-pin SOP-EP (150mil) Outline Dimensions  | 18 |

#### **Features**

- Frequency bands: 315MHz, 433MHz, 868MHz, 915MHz

- Supports OOK/FSK modulation

- Supports 2-wire I2C interface

- Operating voltage range of 2.2V~3.6V

- Programmable OOK symbol rate up to 25ksps

- Programmable FSK data rate up to 50kbps

- $0.25\mu A$  deep sleep mode current with data retention

- TX current consumption @ 433MHz:

- 17mA @ 10dBm POUT (FSK)

- 11mA @ 10dBm POUT (OOK, 50% duty cycle)

- · On-chip VCO and Fractional-N synthesizer with integrated loop filter

- Supports low cost 16MHz crystal

- Supports hardware control mode MCU is not required for radio control

- Integrated 64×1-bit FUSE Data Memory

- Package type: 8-pin SOP-EP

### **Abbreviation Notes**

- TX: RF Transmitter

- SX: Synthesizer

- · XO: External Crystal

- PA: Power Amplifier

- · OOK: On-Off Keying

- FSK: Frequency Shift Keying

- VCO: Voltage Control Oscillator

- MMD: Multi-Mode Divider

- XTAL: External Crystal

# **Development Tools**

For rapid product development and to simplify device parameter setting, Holtek has provided relevant development tools which users can download from the following link:

https://www.holtek.com/rf-workshop

## **General Description**

The BC2102 is a low cost sub-GHz OOK/FSK transmitter for wireless applications in the 315MHz, 433MHz, 470MHz, 868MHz and 915MHz frequency bands. It is a highly integrated and low cost solution for one-way transmitters. It only needs a crystal, a few external capacitors and a few PA output matching components on PCB to form a complete RF solution.

The BC2102 consists of a highly integrated fractional-N Synthesizer and a Class-E Power Amplifier (PA). As it adopts a fractional-N synthesizer, the users can potentially design their transmitters to operate at a wider frequency range. A class-E PA can deliver up to +13dBm output power. With proper setting through an external MCU, the BC2102 can support OOK and FSK modulation with symbol rate of up to 25ksps and data rate of up to 50kbps, respectively.

To minimize power consumption, the BC2102 provides a data tracking function. After no input data is detected during a preset time which can be adjusted through MCU, the BC2102 will return to the deep sleep mode.

These features can be easily programmed through I<sup>2</sup>C interface or internal FUSE. With these combined features the BC2102 can provide a power-saving and cost effective solution for a wide range of wireless applications.

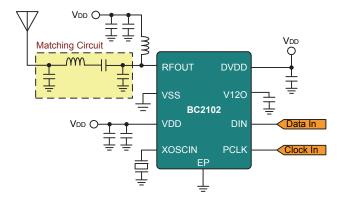

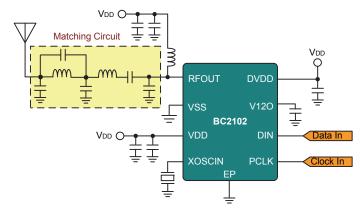

# **Block Diagram**

### Pin Assignment

Rev. 2.00 4 May 07, 2024

## **Pin Description**

| Pin No. | Pin Name       | Function | Type | Description                                     |

|---------|----------------|----------|------|-------------------------------------------------|

| 1       | RFOUT          | PA_OUT   | AO   | RF power amplifier output                       |

| 2       | VSS            | PA_GND   | PWR  | Analog ground                                   |

| 3       | VDD            | VDD      | PWR  | Analog power supply                             |

| 4       | XOSCIN         | Crystal  | Al   | External crystal input                          |

|         |                | PCLK     | I    | Clock input                                     |

| 5       | PCLK/SCL/ICPCK | SCL      | I    | I <sup>2</sup> C clock input                    |

|         |                | ICPCK    | I    | ICP clock input pin                             |

|         |                | DIN      | I    | RF transmitter data input                       |

| 6       | DIN/SDA/ICPDA  | SDA      | I    | I <sup>2</sup> C data input                     |

|         |                | ICPDA    | I    | ICP data input pin                              |

| 7       | V12O           | LDO_OUT  | PWR  | LDO output, must be connected a 0.1µF capacitor |

| 8       | DVDD           | VDD      | PWR  | Digital power supply                            |

| _       | VSS/EP(*)      | Ground   | PWR  | Exposed pad, must be connected to ground        |

Note: I: Digital Input; O: Digital Output; AI: Analog Input;

AO: Analog Output;

PWR: Power.

# **Absolute Maximum Ratings**

| Supply Voltage        | $V_{SS}$ -0.3V to $V_{SS}$ +3.6V        |

|-----------------------|-----------------------------------------|

| Voltage on I/O pins   | V <sub>SS</sub> -0.3V to $V_{DD}$ +0.3V |

| Storage Temperature   | -60°C to 150°C                          |

| Operating Temperature | -40°C to 85°C                           |

| ESD HBM               | ±2kV                                    |

<sup>\*</sup> This device is ESD sensitive. HBM (Human Body Mode) is based on the MIL-STD-883.

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those has listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

<sup>\*: 1.</sup> The VSS/EP pin located at the exposed pad.

<sup>2.</sup> The backside plate of EP shall be well soldered to ground on PCB, otherwise it will downgrade RF performance.

## D.C. Characteristics

Ta=25°C,  $V_{DD}$ =3.3V,  $f_{XTAL}$ =16MHz, OOK/FSK modulation with Matching circuit, PAOUT is powered by  $V_{DD}$ =3.3V, unless otherwise noted.

| Symbol               | Parameter                                       | Test Conditions                 | Min.                | Тур. | Max.                | Unit |  |  |  |

|----------------------|-------------------------------------------------|---------------------------------|---------------------|------|---------------------|------|--|--|--|

| T <sub>OP</sub>      | Operating Temperature                           | _                               | -40                 | _    | 85                  | °C   |  |  |  |

| $V_{DD}$             | Supply Voltage                                  | _                               | 2.2                 | 3.3  | 3.6                 | V    |  |  |  |

| $T_FP$               | FUSE Programming Temperature                    | _                               | _                   | 25   | _                   | °C   |  |  |  |

| Digital I/           | Os                                              |                                 |                     |      |                     |      |  |  |  |

| VIH                  | High Level Input Voltage                        | _                               | 0.7×V <sub>DD</sub> | _    | $V_{DD}$            | V    |  |  |  |

| VIL                  | Low Level Input Voltage                         | _                               | 0                   | _    | 0.3×V <sub>DD</sub> | V    |  |  |  |

| Vон                  | High Level Output Voltage                       | I <sub>он</sub> =-5mA           | 0.8×V <sub>DD</sub> | _    | $V_{DD}$            | V    |  |  |  |

| VoL                  | Low Level Output Voltage                        | I <sub>OL</sub> =5mA            | 0                   | _    | 0.2×V <sub>DD</sub> | V    |  |  |  |

| Current              | Consumption                                     |                                 |                     |      |                     |      |  |  |  |

| I <sub>Sleep</sub>   | Deep Sleep Mode Current Consumption             | _                               | _                   | 0.25 | 0.40                | μA   |  |  |  |

| I <sub>Standby</sub> | Idle Mode Current Consumption                   | XTAL on, PA off, Synthesizer on | _                   | 6.5  | _                   | mA   |  |  |  |

|                      |                                                 | P <sub>RF</sub> =0dBm           | _   11   _          |      | _                   |      |  |  |  |

|                      | High Data Current Consumption @ 315MHz (Data=1) | P <sub>RF</sub> =10dBm          | _                   | 19   | _                   | mA   |  |  |  |

|                      | (Bata-1)                                        | P <sub>RF</sub> =13dBm          | _                   | 24   | _                   |      |  |  |  |

|                      |                                                 | P <sub>RF</sub> =0dBm           | _                   | 11   | _                   |      |  |  |  |

|                      | High Data Current Consumption @ 433MHz (Data=1) | P <sub>RF</sub> =10dBm          | _                   | 17   | _                   | mA   |  |  |  |

|                      | (Bata-1)                                        | P <sub>RF</sub> =13dBm          | _                   | 24   | _                   |      |  |  |  |

| I <sub>TX</sub>      |                                                 | P <sub>RF</sub> =0dBm           | _                   | 11   | _                   |      |  |  |  |

|                      | High Data Current Consumption @ 868MHz (Data=1) | P <sub>RF</sub> =10dBm          | _                   | 19   | _                   | mA   |  |  |  |

|                      | (Bata-1)                                        | P <sub>RF</sub> =13dBm          | _                   | 24   | _                   |      |  |  |  |

|                      |                                                 | P <sub>RF</sub> =0dBm           | _                   | 12   | _                   |      |  |  |  |

|                      | High Data Current Consumption @ 915MHz (Data=1) | P <sub>RF</sub> =10dBm          | _                   | 20   | _                   | mA   |  |  |  |

|                      | US O TOWN 12 (Data-1)                           | P <sub>RF</sub> =13dBm          | _                   | 25   | _                   |      |  |  |  |

| Pull-higl            | n Resistance                                    |                                 |                     |      |                     |      |  |  |  |

| R <sub>PH</sub>      | Pull-high Resistance for I/O Ports              | 3.3V                            | _                   | 33   | _                   | kΩ   |  |  |  |

## A.C. Characteristics

#### **RF Characteristics**

Ta=25°C,  $V_{DD}$ =3.3V,  $f_{XTAL}$ =16MHz, OOK/FSK modulation with Matching circuit, PAOUT is powered by  $V_{DD}$ =3.3V, unless otherwise noted.

| Symbol           | Parameter                  | Test Conditions                             | Min. | Тур.   | Max. | Unit  |

|------------------|----------------------------|---------------------------------------------|------|--------|------|-------|

|                  | er Characteristics         |                                             |      | -71-   |      |       |

|                  |                            | 315MHz band                                 | _    | 315    | _    |       |

| r                |                            | 433MHz band                                 | _    | 433.92 | _    | MHz   |

| $f_{RF}$         | RF Frequency Band          | 868MHz band                                 | _    | 868.35 | _    | IVIHZ |

|                  |                            | 915MHz band                                 | _    | 915 —  |      |       |

| SR               | Symbol Rate                | OOK modulation                              | 0.5  | _      | 25   | ksps  |

| DR               | Data Rate                  | FSK modulation (@f <sub>DEV</sub> =12.5kHz) | 0.5  | _      | 50   | kbps  |

|                  | DE Transcrit Outrout Davis | 433MHz band                                 | 0    | _      | 13   | -ID   |

| $P_{RF}$         | RF Transmit Output Power   | 868MHz band                                 | 0    | _      | 13   | dBm   |

| t <sub>ST</sub>  | RF Transmit Settling Time  | Standby mode to Transmit mode               | _    | 370    | _    | μs    |

| ERook            | OOK Extinction Ratio       | OOK modulation depth                        | _    | 70     | _    | dB    |

| f <sub>DEV</sub> | Frequency Deviation        | FSK modulation @ fxtAL=16MHz                | 2    | _      | 100  | kHz   |

Rev. 2.00 6 May 07, 2024

| Symbol             | Parameter                                      | Test Conditions                                                                    | Min.  | Тур. | Max. | Unit  |

|--------------------|------------------------------------------------|------------------------------------------------------------------------------------|-------|------|------|-------|

|                    | Output Blanking                                | From Deep Sleep to Transmit mode                                                   | _     | _    | 1    | Ms    |

|                    | One Shot Delay Time                            | OOK/FSK                                                                            | 4     | _    | 32   | ms    |

|                    |                                                | f<1GHz                                                                             | _     | _    | -36  |       |

|                    |                                                | 47MHz <f<74mhz< td=""><td></td><td></td><td></td><td></td></f<74mhz<>              |       |      |      |       |

| S.E. <sub>TX</sub> | TX Spurious Emission (P <sub>RF</sub> = 10dBm) | 87.5MHz <f<118mhz< td=""><td></td><td></td><td>-54</td><td>dBm</td></f<118mhz<>    |       |      | -54  | dBm   |

| S.E.TX             | TA Spurious Emission (PRF – Todbin)            | 174MHz <f<230mhz< td=""><td>_</td><td>_</td><td>-54</td><td>ubiii</td></f<230mhz<> | _     | _    | -54  | ubiii |

|                    |                                                | 470MHz <f<862mhz< td=""><td></td><td></td><td></td><td></td></f<862mhz<>           |       |      |      |       |

|                    |                                                | 2 <sup>nd</sup> , 3 <sup>rd</sup> Harmonic                                         | _     | _    | -30  |       |

| LO Chara           | cteristics                                     |                                                                                    |       |      |      |       |

|                    |                                                | 315MHz band                                                                        | 290 — |      | 335  | ]     |

| f <sub>LO</sub>    | RF Frequency Coverage Range                    | 433MHz band                                                                        | 415   | _    | 490  | MHz   |

|                    |                                                | 868MHz band                                                                        | 830   | _    | 960  |       |

| f <sub>STEP</sub>  | LO Frequency Resolution                        | _                                                                                  | _     | _    | 1    | kHz   |

|                    | 433MHz Phase Noise                             | @ 100kHz offset                                                                    | _     | -76  | _    |       |

| PNLO               | 433WINZ FITASE NOISE                           | @ 1MHz offset                                                                      |       | -104 | _    | dBc/  |

| FINLO              | 868MHz Phase Noise                             | @ 100kHz offset                                                                    | _     | -70  | _    | Hz    |

|                    | ODOIVINZ FIIASE NOISE                          | @ 1MHz offset                                                                      |       | -100 | _    |       |

| Crystal O          | scillator                                      |                                                                                    |       |      |      |       |

| f <sub>XTAL</sub>  | XTAL Frequency                                 | _                                                                                  | _     | 16   | _    | MHz   |

| ESR                | XTAL Equivalent Series Resistance              | _                                                                                  | _     | _    | 100  | Ω     |

| CLOAD              | XTAL Capacitor Load                            | _                                                                                  | _     | 16   | _    | pF    |

| TOL (Note)         | XTAL Tolerance                                 | _                                                                                  | -20   | _    | +20  | ppm   |

| t <sub>a</sub>     | XTAL Startup Time                              | 49US                                                                               | _     | _    | 1    | ms    |

| t <sub>su</sub>    | ATAL Startup Time                              | 3225SMD                                                                            |       | 3    | 1    | ms    |

Note: This is the total tolerance including (1) Initial tolerance (2) Crystal loading (3) Aging and (4) Temperature dependence.

The acceptable crystal tolerance depends on RF frequency and channel spacing/band width.

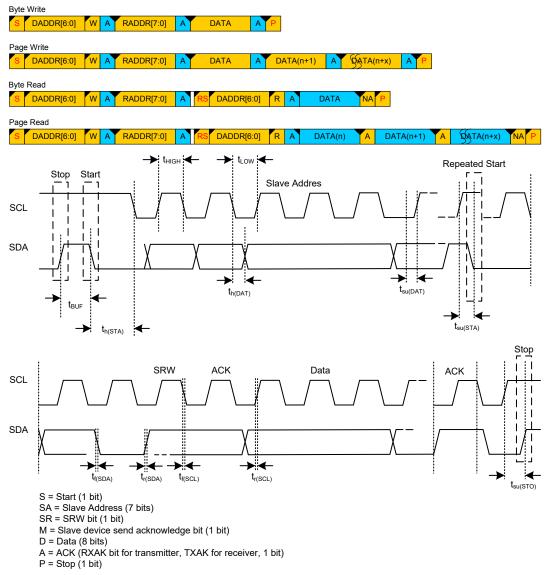

### I<sup>2</sup>C Characteristics

Ta=25°C

| Symbol                 | Parameter                                      | Test Conditions | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------------------------|-----------------|------|------|------|------|

| I <sup>2</sup> C Chara | cteristics                                     |                 |      |      |      |      |

| f <sub>SCL</sub>       | Serial Clock Frequency                         | _               | _    | _    | 1    | MHz  |

| t <sub>BUF</sub>       | Bus Free Time between Stop and Start Condition | SCL=1MHz        | 250  | _    | _    | ns   |

| t <sub>LOW</sub>       | SCL Low Time                                   | SCL=1MHz        | 500  | _    | _    | ns   |

| t <sub>HIGH</sub>      | SCL High Time                                  | SCL=1MHz        | 500  | _    | _    | ns   |

| t <sub>su(DAT)</sub>   | Data Setup Time                                | SCL=1MHz        | 100  | _    | _    | ns   |

| t <sub>su(STA)</sub>   | Start Condition Setup Time                     | SCL=1MHz        | 250  | _    | _    | ns   |

| t <sub>su(STO)</sub>   | Stop Condition Setup Time                      | SCL=1MHz        | 250  | _    | _    | ns   |

| t <sub>h(DAT)</sub>    | Data Hold Time                                 | SCL=1MHz        | 100  | _    | _    | ns   |

| t <sub>h(STA)</sub>    | Start Condition Hold Time                      | SCL=1MHz        | 250  | _    | _    | ns   |

| t <sub>r(SCL)</sub>    | Rise Time of SCL Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |

| t <sub>f(SCL)</sub>    | Fall Time of SCL Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |

| t <sub>r(SDA)</sub>    | Rise Time of SDA Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |

| t <sub>f(SDA)</sub>    | Fall Time of SDA Signal                        | SCL=1MHz        | _    | _    | 100  | ns   |

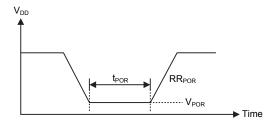

#### **Power on Reset Electrical Characteristics**

Ta=25°C

| Symbol           | nbol Parameter –                                                                    |   | est Conditions | Min.    | Typ. | Max.   | Unit  |

|------------------|-------------------------------------------------------------------------------------|---|----------------|---------|------|--------|-------|

| Symbol           |                                                                                     |   | Conditions     | IVIIII. | iyp. | IVIAX. | Ollit |

| V <sub>POR</sub> | V <sub>DD</sub> Start Voltage to Ensure Power-on Reset                              | _ | _              | _       | _    | 100    | mV    |

| RRPOR            | V <sub>DD</sub> Rising Rate to Ensure Power-on Reset                                | _ | _              | 0.035   | _    | _      | V/ms  |

| t <sub>POR</sub> | Minimum Time for V <sub>DD</sub> Stays at V <sub>POR</sub> to Ensure Power-on Reset | _ | _              | 1       | _    | _      | ms    |

### **Functional Description**

The BC2102 is a low cost sub-GHz OOK/FSK transmitter for wireless applications in the 315MHz, 433MHz, 470MHz, 868MHz and 915MHz frequency bands. It consists of a highly integrated fractional-N Synthesizer and a Class-E Power Amplifier (PA).

The RF frequency is generated by a fully integrated fractional-N Synthesizer which includes RF VCO, loop filter and Digital controlled XO (DCXO). A fractional-N synthesizer allows users to extend their applications to a wider frequency range with the same XO.

The transmit session is a VCO direct modulation architecture. Different from the conventional direct-up conversion transmitter, the FSK modulation signal is fed into the VCO directly to take advantage of fractional-N synthesizer. As a result, both layout area and current consumption are much smaller. The modulated signal, generated by VCO, is fed into a Class-E PA and the maximum output power can be up to +13dBm.

For OOK modulation applications, the BC2102 provides an optimized PA ramping up and down feature to avoid the power spreading in the frequency domain.

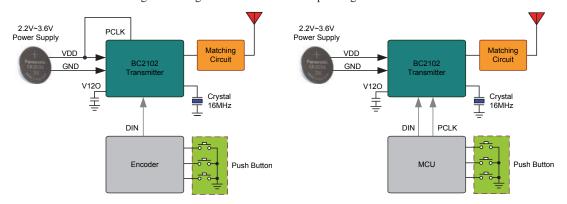

#### **Solution Overview**

The BC2102 provides a 64×1-bit FUSE data memory, similar to One-time Programming (OTP) Non-volatile Memory.

If the FUSE is un-programmed, which can be detected by checking the EFPGM bit in the CFG7 register, the user should connect the device to an MCU and setup the relevant RF registers configuration in the I<sup>2</sup>C Mode using an I<sup>2</sup>C interface. However, the registers will be reset to their initial state when the device is powered off.

For devices with programmed FUSE, users can implement a complete and versatile RF transmitter system to work together with an external MCU or Encoder. The corresponding application solutions are shown as below. Note that when EFPGM bit is low the device can only be connected to an external MCU.

If the device is connected with an Encoder, the FUSE data will be automatically copied to the corresponding registers. After a delay time, the encoder can send data to the device through the DIN pin and thus start a transmission sequence.

Rev. 2.00 8 May 07, 2024

If the device is connected to an MCU, the same function aforementioned can also be implemented. The difference is that the MCU can configure the frequency, power and other parameters by setting the relevant registers using an I<sup>2</sup>C interface when operating in the I<sup>2</sup>C Mode.

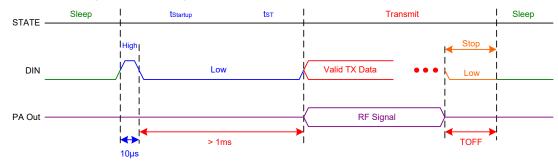

#### **State Control**

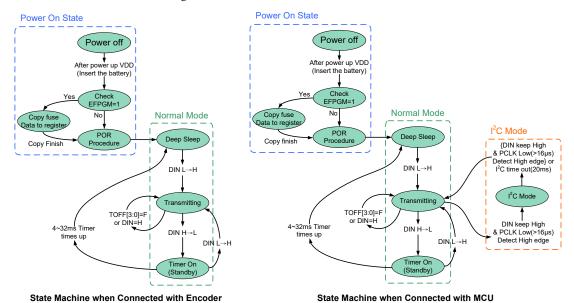

The BC2102 has integrated state machines that control the state transition between modes.

# Power On State

After power-on, if the EFPGM bit state is high, the FUSE data will be automatically copied to the corresponding registers. When completed the device will enter the Deep Sleep Mode after a delay time. Note that the device will directly enter the Deep Sleep Mode after a delay time if the EFPGM bit is low.

#### **Normal Mode**

After a power-on reset operation, the device enters the Deep Sleep Mode. Data will be transmitted if the DIN pin is pulled high or the pulse on the PCLK pin changes from high to low. When data transmission is finished and the DIN pin state changes from high to low, the device will enter the Standby state and the Timer, whose timeout period is determined by DLY\_TOFF bits in the CFG1 register, will turn on and start to count. The device will return to the Deep Sleep Mode when the

Rev. 2.00 9 May 07, 2024

Timer overflows. However, it should be noted that when the DLY\_TOFF[3:0] bit value is "1111", the device will start to transmit again without entering the Deep Sleep Mode once the DIN pin state changes from low to high.

TX Enabled by DIN Pin

#### I<sup>2</sup>C Mode

If the device is connected to an external MCU, then the  $I^2C$  mode can be used. When the SCL line (Pin 5) is pulled low for more than  $16\mu s$  ( $t_{ENI2C}$ ), the device will enter the  $I^2C$  Mode from the Normal Mode, during which the external control register can configure the special function registers in the device using  $I^2C$  commands. When the device receives a correct  $I^2C$  STOP signal followed by the SCL line being pulled low for more than  $16\mu s$ , the device will return to the Normal Mode.

In the I<sup>2</sup>C Mode, the MCU can configure the internal relevant registers using I<sup>2</sup>C serial programming. The transmitter only supports the I<sup>2</sup>C format for byte write, page write, byte read and page read format. The transmission procedure is shown as below.

It should be noted that the  $I^2C$  is a non-standard  $I^2C$  interface, which only supports a single device for connection.

Symbol definition:

- S: Start symbol

- RS: Repeat Start

- P: Stop symbol

- DADDR[6:0]: device address, 21h

- R/W: read write select, R(0): write, (1): read

- RADDR[7:0]: register address

- ACK: A(0):ACK, NA(1):NAK

- Bus Direction: host to device: device to host: Edge to I<sup>2</sup>C Start I<sup>2</sup>C Stop >16us \_>16µs PCLK/SCI DIN/SDA >1ms >t<sub>OFF</sub> Enter Sleep Normal Mode into I<sup>2</sup>C Mode I<sup>2</sup>C Serial Programming Sleep Mode I<sup>2</sup>C Mode Terminate

I<sup>2</sup>C Serial Programming

Rev. 2.00 10 May 07, 2024

I<sup>2</sup>C Communication Timing Diagram

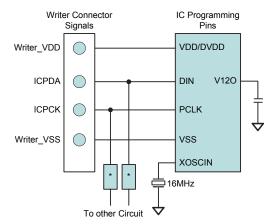

#### **Programming Methodology**

The device programming interface should utilise an adaptor with an integrated 16MHz crystal.

| Program Function  | Pin Name                | Pin Description  |

|-------------------|-------------------------|------------------|

| ICPCK             | PCLK (Pin5)             | ICP clock        |

| ICPDA             | DIN (Pin)               | ICP Data/Address |

| VDD               | VDD (Pin3), DVDD (Pin8) | Power supply     |

| VSS, EP           | VSS (Pin2), Exposed-Pad | Ground           |

| XTAL IN (Adaptor) | XOSCIN (Pin4)           | IC system clock  |

When programming, the device needs to be located on a Socket with a 16MHz crystal connected between Pin XOSCIN and ground. Holtek provides an e-Link or e-WriterPro tool for communication with the PC. Between the e-Link and the device there are four interconnecting lines, namely VDD, VSS, PCLK and DIN pins.

Note: \* may be resistor or capacitor – the resistance of \* must be greater than  $1k\Omega$  and the capacitance of \* must be less than 1nF.

# **Register Map**

When connected to an external MCU, the device can be setup and operated using a series of internal registers. Device commands and data are written to and read from the device using its internal I<sup>2</sup>C bus. This list provides a summary of all internal registers. Their detailed operation is described under their relevant section in the functional description.

| Address | Register |         |            |          | Bit   |          |          | -       |          |

|---------|----------|---------|------------|----------|-------|----------|----------|---------|----------|

| Address | Name     | 7       | 6          | 5        | 4     | 3        | 2        | 1       | 0        |

| 00h     | CFG0     | Settin  | g0         |          |       | XO_TR    | RIM[5:0] |         |          |

| 01h     | CFG1     |         | DLY_TOP    | F[3:0]   |       |          | Sett     | ing1    |          |

| 02h     | CFG2     |         |            |          | FDEV[ | 7:0]     |          |         |          |

| 03h     | CFG3     | FSK_SEL |            | Setting2 |       |          | TXPW     | /R[3:0] |          |

| 04h     | CFG4     |         |            | D_N[5    | 5:0]  |          |          | BAND_   | SEL[1:0] |

| 05h     | CFG5     |         |            |          | D_K[1 | 1:4]     |          |         |          |

| 06h     | CFG6     |         | D_K[19:12] |          |       |          |          |         |          |

| 07h     | CFG7     | EFPGM   |            |          |       | Setting3 |          |         |          |

If the Fuse is un-programmed, the BC2102 device will have a default state described in the following, determined by register initial values.

Modulation Mode: OOK

Operating Frequency: 433.92MHz

TX Output Power: 10dBm

XTAL Capacitor Load: 16.651pF Power Off Delay Time: 32ms

Rev. 2.00 12 May 07, 2024

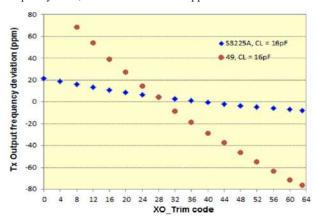

#### • CFG0: Configuration Control Register 0

| Address | Bit           | 7    | 6    | 5            | 4   | 3 | 2 | 1 | 0 |

|---------|---------------|------|------|--------------|-----|---|---|---|---|

|         | Name          | Sett | ing0 | XO_TRIM[5:0] |     |   |   |   |   |

| 00h     | R/W           | R/W  | R/W  |              | R/W |   |   |   |   |

|         | Initial Value | 1    | 0    | 1            | 0   | 0 | 0 | 0 | 0 |

Bit 7~6 **Setting0**: Must be [0b10]

Bit 5~0 **XO\_TRIM[5:0]**: Trim value of the internal capacitor array for different crystal C<sub>LOAD</sub> Based on XO fabricated by YOKETAN corporation.

49US~16MHz~XO~w/~16pF~Cload: The default setting is 1B. Within  $\pm 40ppm$  frequency error, 1 trim code shift -2.88ppm.

3225SMD 16MHz XO w/ 16pF Cload: The default setting is 28. Within  $\pm 20$ ppm frequency error, 1 trim code shift -0.37ppm.

#### • CFG1: Configuration Control Register 1

| Address | Bit           | 7 | 6      | 5        | 4 | 3 | 2    | 1    | 0 |

|---------|---------------|---|--------|----------|---|---|------|------|---|

|         | Name          |   | DLY_TC | DFF[3:0] |   |   | Sett | ing1 |   |

| 01h     | R/W           |   | R/     | W        |   |   | R    | W    |   |

|         | Initial Value | 1 | 1      | 1        | 0 | 0 | 0    | 0    | 1 |

Bit 7~4 **DLY\_TOFF[3:0]**: Transmitter Auto Power Off Delay Time

$t = 2ms \times (DLY\_TOFF[3:0]+2)$

0000: 4ms

0001: 6ms

0010: 8ms

:

1110: 32ms

1111: Infinite – Never enter the Deep Sleep Mode

Bit 3~0 **Setting1**: Must be [0b0001]

#### • CFG2: Configuration Control Register 2

| Address | Bit           | 7 | 6   | 5 | 4    | 3      | 2 | 1 | 0 |

|---------|---------------|---|-----|---|------|--------|---|---|---|

|         | Name          |   |     |   | FDE\ | /[7:0] |   |   |   |

| 02h     | R/W           |   | R/W |   |      |        |   |   |   |

|         | Initial Value | 0 | 1   | 1 | 0    | 0      | 1 | 1 | 0 |

Bit 7~0 **FDEV[7:0]**: Frequency deviation for FSK

External Crystal = 16MHz, FDEV =  $(f_{DEV} \times 2^{15}/Fxtal)$ ;  $f_{XTAL} = 16MHz$

Examples are as follows:

Default FDEV[7:0] =  $01100110 \rightarrow Decimal 102$

External Crystal = 16MHz

$f_{DEV}$  (Frequency deviation) =  $f_{DEV} \times (16M/2^{15})$

$f_{DEV}$  (Frequency deviation) =  $102 \times (16M/32768) = 49.8kHz$

#### • CFG3: Configuration Control Register 3

| Address | Bit           | 7       | 6        | 5   | 4 | 3          | 2 | 1 | 0 |

|---------|---------------|---------|----------|-----|---|------------|---|---|---|

|         | Name          | FSK_SEL | Setting2 |     |   | TXPWR[3:0] |   |   |   |

| 03h     | R/W           | R/W     |          | R/W |   |            | R | W |   |

|         | Initial Value | 0       | 1        | 0   | 0 | 1          | 0 | 0 | 0 |

Bit 7 FSK\_SEL: FSK Mode Enable

0: OOK 1: FSK

Bit 6~4 **Setting 2**: Must be [0b100] Bit 3~0 **TXPWR[3:0**]: RF Output Power

The device has several output power values which are 0, 5, 10, and 13dBm.

| TXPWR[3:0]   | RF Output Power |  |  |  |

|--------------|-----------------|--|--|--|

| <u>00</u> 00 | 0dBm            |  |  |  |

| <u>01</u> 00 | 5dBm            |  |  |  |

| <u>10</u> 00 | 10dBm           |  |  |  |

| <u>11</u> 00 | 13dBm           |  |  |  |

| TXPWR[3:0]   | RF Output Power Fine Tune Level |

|--------------|---------------------------------|

| XX <u>00</u> | 0                               |

| XX <u>01</u> | 1                               |

| XX <u>10</u> | 2                               |

| XX <u>11</u> | 3                               |

Note that the adjust range: Level 3 > Level 2 > Level 1 > Level 0.

Note: Output power level could vary due to different matching components and placement on the PCB. The matching variation could significantly impact the output power level below +5dBm setting.

#### CFG4: Configuration Control Register 4

| Address | Bit           | 7                      | 6       | 5 | 4 | 3 | 2 | 1 | 0        |

|---------|---------------|------------------------|---------|---|---|---|---|---|----------|

|         | Name          | D_N[5:0] BAND_SEL[1:0] |         |   |   |   |   |   | SEL[1:0] |

| 04h     | R/W           |                        | R/W R/W |   |   |   |   |   |          |

|         | Initial Value | 0                      | 1       | 0 | 1 | 1 | 0 | 0 | 1        |

Bit 7~2 **D\_N[5:0]**: Integer of dividend for MMD

Bit 1~0 BAND\_SEL[1:0]: Band Frequency Coarse Control

| BAND_SEL | Frequency |

|----------|-----------|

| 00       | 315MHz    |

| 01       | 433MHz    |

| 10       | 868MHz    |

| 11       | 915MHz    |

Note that the BAND\_SEL only select an approximate frequency range while the exact frequency value is determined by the D\_N and D\_K bit fields.

Rev. 2.00 14 May 07, 2024

#### • CFG5: Configuration Control Register 5

| Address | Bit           | 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------------|-----------|---|---|---|---|---|---|---|

|         | Name          | D_K[11:4] |   |   |   |   |   |   |   |

| 05h     | R/W           | R/W       |   |   |   |   |   |   |   |

|         | Initial Value | 0         | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

#### • CFG6: Configuration Control Register 6

| Address | Bit           | 7          | 6   | 5 | 4 | 3 | 2 | 1 | 0 |

|---------|---------------|------------|-----|---|---|---|---|---|---|

|         | Name          | D_K[19:12] |     |   |   |   |   |   |   |

| 06h     | R/W           |            | R/W |   |   |   |   |   |   |

|         | Initial Value | 0          | 0   | 1 | 1 | 1 | 1 | 0 | 1 |

**D\_K[19:4]**: 16-bit Fractional of dividend for MMD

D N&D K example.

X'TAL=16MHz and TX band =433MHz

1. D\_N  $\rightarrow$  (433M×Divider)/16M=54.125 Take the integer part  $\rightarrow$  D\_N=54-32=22  $\rightarrow$  010110

2. D\_K  $\rightarrow$  (433M×Divider)/16M=54.125 Take the fractional part  $\rightarrow$  D\_K=0.125×2<sup>20</sup>=131072  $\rightarrow$  0010-0000-0000

3. The example frequency can be referred in the following table.

| Band_SEL | Frequency | Divider | X'TAL | D_N[5:0] | D_K[19:4]           |

|----------|-----------|---------|-------|----------|---------------------|

| 315MHz   | 315MHz    | 2       | 16MHz | 000111   | 0110-0000-0000-0000 |

| 433MHz   | 433MHz    | 2       | 16MHz | 010110   | 0010-0000-0000-0000 |

| 433MHz   | 433.92MHz | 2       | 16MHz | 010110   | 0011-1101-0111-0000 |

| 868MHz   | 868MHz    | 1       | 16MHz | 010110   | 0100-0000-0000-0000 |

| 915MHz   | 915MHz    | 1       | 16MHz | 011001   | 0011-0000-0000-0000 |

#### • CFG7: Configuration Control Register 7

| Address | Bit           | 7     | 6 | 5 | 4 | 3        | 2 | 1 | 0 |

|---------|---------------|-------|---|---|---|----------|---|---|---|

|         | Name          | EFPGM |   |   |   | Setting3 |   |   |   |

| 07h     | R/W           | R     |   |   |   | R/W      |   |   |   |

|         | Initial Value | 0     | 1 | 0 | 0 | 1        | 0 | 1 | 1 |

Bit 7 **EFPGM**: Fuse programmed, read only for I<sup>2</sup>C

0: FUSE is not programmed – FUSE data is not mapped to the configuration register 1: FUSE is programmed – FUSE data is mapped to the configuration register

Bit 6~0 **Setting3**: Must be [0b1001011]

# **Application Circuits**

# 433MHz Application Example

## **Evaluation Board Circuit**

Rev. 2.00 16 May 07, 2024

# **Package Information**

Note that the package information provided here is for consultation purposes only. As this information may be updated at regular intervals users are reminded to consult the <u>Holtek website</u> for the latest version of the <u>Package/Carton Information</u>.

Additional supplementary information with regard to packaging is listed below. Click on the relevant section to be transferred to the relevant website page.

- Package Information (include Outline Dimensions, Product Tape and Reel Specifications)

- The Operation Instruction of Packing Materials

- Carton information

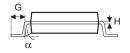

# 8-pin SOP-EP (150mil) Outline Dimensions

| Symbol |       | Dimensions in inch |       |  |  |  |  |  |  |

|--------|-------|--------------------|-------|--|--|--|--|--|--|

| Symbol | Min.  | Nom.               | Max.  |  |  |  |  |  |  |

| A      | _     | 0.236 BSC          | _     |  |  |  |  |  |  |

| В      | _     | 0.154 BSC          | _     |  |  |  |  |  |  |

| С      | 0.012 | _                  | 0.020 |  |  |  |  |  |  |

| C'     | _     | 0.193 BSC          | _     |  |  |  |  |  |  |

| D      | _     | _                  | 0.069 |  |  |  |  |  |  |

| D1     | 0.076 | _                  | 0.090 |  |  |  |  |  |  |

| Е      | _     | 0.050 BSC          | _     |  |  |  |  |  |  |

| E2     | 0.076 | _                  | 0.090 |  |  |  |  |  |  |

| F      | 0.000 | _                  | 0.006 |  |  |  |  |  |  |

| G      | 0.016 | _                  | 0.050 |  |  |  |  |  |  |

| Н      | 0.004 | _                  | 0.010 |  |  |  |  |  |  |

| α      | 0°    | _                  | 8°    |  |  |  |  |  |  |

| Complete | Dimensions in mm |          |      |  |  |  |  |  |

|----------|------------------|----------|------|--|--|--|--|--|

| Symbol   | Min.             | Nom.     | Max. |  |  |  |  |  |

| A        | _                | 6.00 BSC | _    |  |  |  |  |  |

| В        | _                | 3.90 BSC | _    |  |  |  |  |  |

| С        | 0.31             | _        | 0.51 |  |  |  |  |  |

| C'       | _                | 4.90 BSC | _    |  |  |  |  |  |

| D        | _                | _        | 1.75 |  |  |  |  |  |

| D1       | 1.94             | _        | 2.29 |  |  |  |  |  |

| E        | _                | 1.27 BSC | _    |  |  |  |  |  |

| E2       | 1.94             | _        | 2.29 |  |  |  |  |  |

| F        | 0.00             | _        | 0.15 |  |  |  |  |  |

| G        | 0.40             | _        | 1.27 |  |  |  |  |  |

| Н        | 0.10             | _        | 0.25 |  |  |  |  |  |

| α        | 0°               | _        | 8°   |  |  |  |  |  |

Note: For this package type, refer to the package information provided here, which will not be updated by the Holtek website.

Rev. 2.00 18 May 07, 2024

Copyright® 2024 by HOLTEK SEMICONDUCTOR INC. All Rights Reserved.

The information provided in this document has been produced with reasonable care and attention before publication, however, HOLTEK does not guarantee that the information is completely accurate. The information contained in this publication is provided for reference only and may be superseded by updates. HOLTEK disclaims any expressed, implied or statutory warranties, including but not limited to suitability for commercialization, satisfactory quality, specifications, characteristics, functions, fitness for a particular purpose, and non-infringement of any thirdparty's rights. HOLTEK disclaims all liability arising from the information and its application. In addition, HOLTEK does not recommend the use of HOLTEK's products where there is a risk of personal hazard due to malfunction or other reasons. HOLTEK hereby declares that it does not authorise the use of these products in life-saving, life-sustaining or safety critical components. Any use of HOLTEK's products in life-saving/sustaining or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold HOLTEK harmless from any damages, claims, suits, or expenses resulting from such use. The information provided in this document, including but not limited to the content, data, examples, materials, graphs, and trademarks, is the intellectual property of HOLTEK (and its licensors, where applicable) and is protected by copyright law and other intellectual property laws. No license, express or implied, to any intellectual property right, is granted by HOLTEK herein. HOLTEK reserves the right to revise the information described in the document at any time without prior notice. For the latest information, please contact us.