# HT32F59041 Datasheet

Enhanced 24-bit A/D Arm® Cortex®-M0+ Flash MCU 64 KB Flash and 8 KB SRAM with 1 MSPS 12-Bit ADC 24-Bit Delta Sigma ADC, DIV, USART, UART, SPI, I<sup>2</sup>C MCTM, GPTM, BFTM, PWM, CRC, RTC and WDT

Revision: V1.00 Date: January 17, 2020

www.holtek.com

# **Table of Contents**

| 1 | General Description                                             | 6    |

|---|-----------------------------------------------------------------|------|

| 2 | Features                                                        | 7    |

|   | Core                                                            | 7    |

|   | On-chip Memory                                                  | 7    |

|   | Flash Memory Controller – FMC                                   | 7    |

|   | Reset Control Unit – RSTCU                                      | 8    |

|   | Clock Control Unit – CKCU                                       | 8    |

|   | Power Management Control Unit – PWRCU                           | 8    |

|   | Real Time Clock – RTC                                           | 9    |

|   | External Interrupt / Event Controller – EXTI                    | 9    |

|   | Hardware Divider – DIV                                          | 9    |

|   | 12-Bit Analog to Digital Converter – ADC                        | 9    |

|   | 24-Bit Delta Sigma Analog to Digital Converter – ΔΣ ADC         | . 10 |

|   | I/O Ports – GPIO                                                | . 10 |

|   | Basic Function Timer – BFTM                                     | . 10 |

|   | Motor Control Timer – MCTM                                      | . 10 |

|   | PWM Generation and Capture Timer – GPTM                         | . 11 |

|   | Pulse Width Modulation – PWM                                    | . 11 |

|   | Watchdog Timer – WDT                                            | . 12 |

|   | Inter-integrated Circuit – I <sup>2</sup> C                     | . 12 |

|   | Serial Peripheral Interface – SPI                               | . 12 |

|   | Universal Synchronous Asynchronous Receiver Transmitter – USART | . 13 |

|   | Universal Asynchronous Receiver Transmitter – UART              | . 13 |

|   | Cyclic Redundancy Check – CRC                                   | . 14 |

|   | Debug Support                                                   |      |

|   | Package and Operation Temperature                               | . 14 |

| 3 | Overview                                                        | 15   |

|   | Device Information                                              | . 15 |

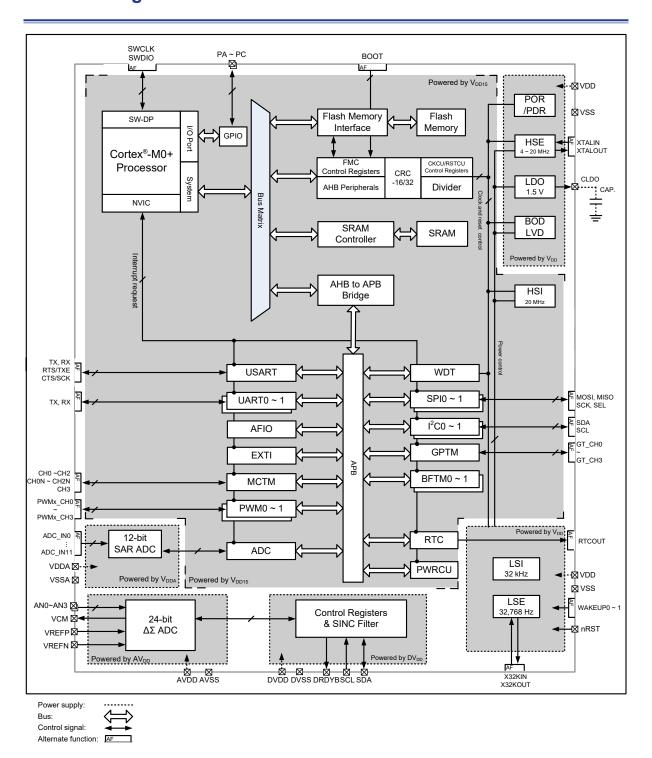

|   | Block Diagram                                                   | . 16 |

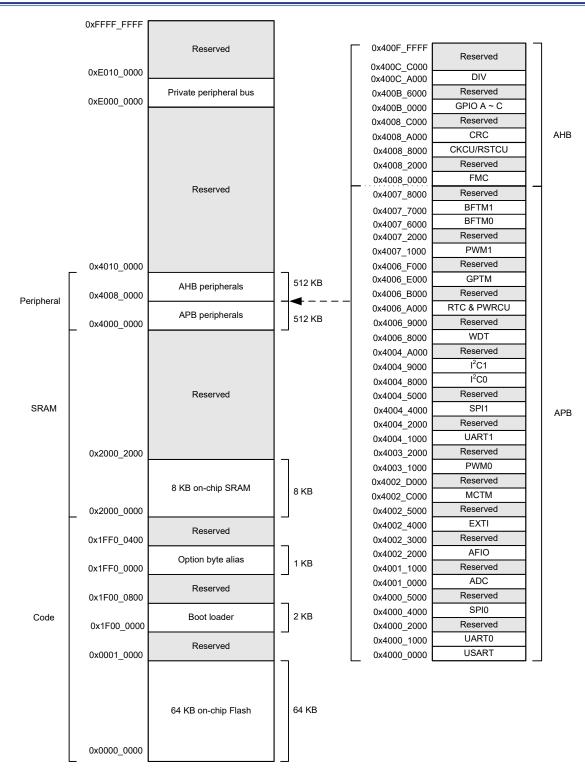

|   | Memory Map                                                      | . 17 |

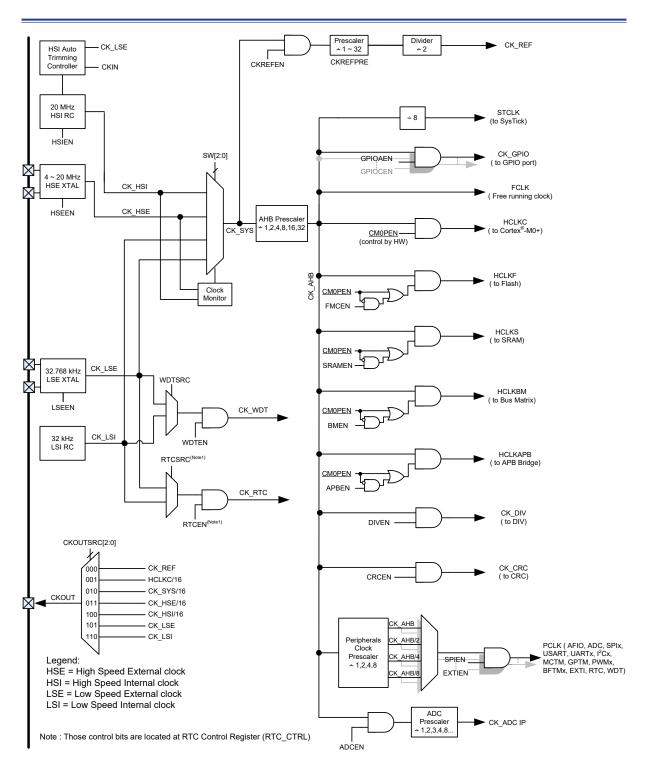

|   | Clock Structure                                                 | . 20 |

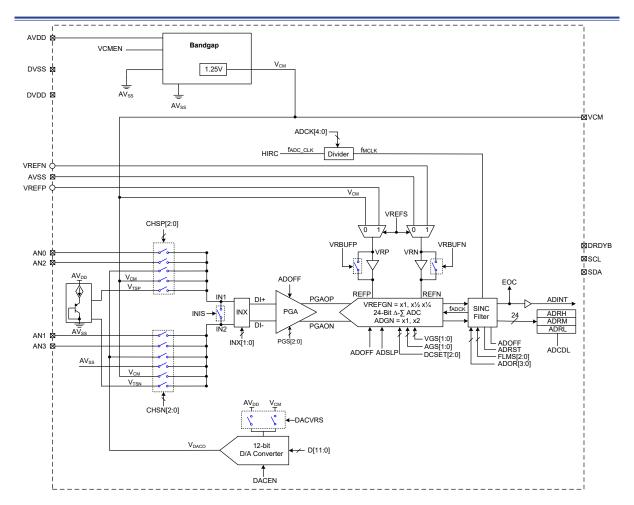

| 4 | 24-Bit Delta Sigma A/D Converter – ΔΣ ADC                       | .21  |

|   | 24-Bit A/D Converter Internal Registers                         | . 22 |

|   | Internal Power Supply                                           | . 23 |

|   | Reference Voltages                                              | . 23 |

|   | Power and Reference Control                   | 24 |

|---|-----------------------------------------------|----|

|   | Oscillator                                    | 25 |

|   | Input Signal Gain Control Amplifier – PGA     | 26 |

|   | 24-Bit Analog to Digital Converter Operation  | 28 |

|   | External Interface Communication              | 35 |

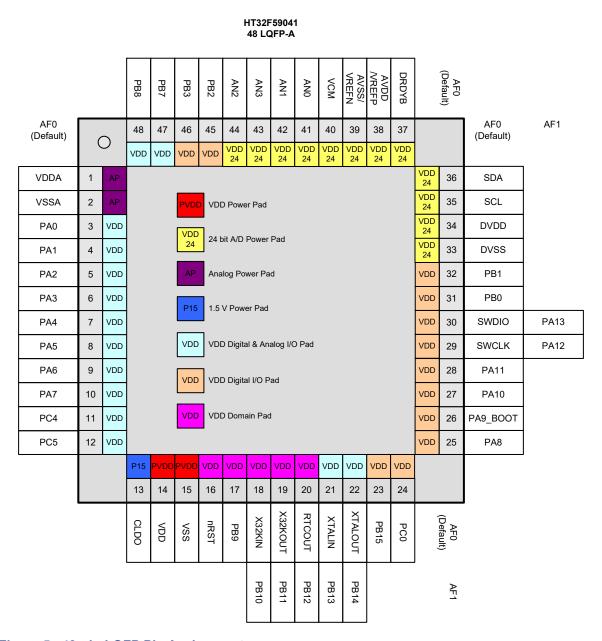

| 5 | Pin Assignment                                | 39 |

| 6 | Electrical Characteristics                    | 43 |

|   | Absolute Maximum Ratings                      | 43 |

|   | Recommended DC Operating Conditions           | 43 |

|   | On-Chip LDO Voltage Regulator Characteristics | 43 |

|   | Power Consumption                             | 44 |

|   | Reset and Supply Monitor Characteristics      | 45 |

|   | External Clock Characteristics                | 46 |

|   | Internal Clock Characteristics                | 47 |

|   | Memory Characteristics                        | 48 |

|   | I/O Port Characteristics                      | 48 |

|   | 12-Bit ADC Characteristics                    | 49 |

|   | 24-Bit ADC Characteristics                    | 51 |

|   | Effective Number of Bits (ENOB)               | 52 |

|   | MCTM/GPTM/PWM Characteristics                 | 54 |

|   | I <sup>2</sup> C Characteristics              | 54 |

|   | SPI Characteristics                           | 55 |

| 7 | Package Information                           | 57 |

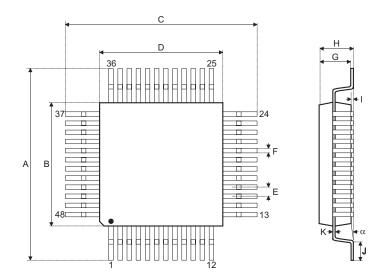

|   | 48-pin LQFP (7mm × 7mm) Outline Dimensions    | 58 |

# **List of Tables**

| Table 1. | Features and Peripheral List                       | 15 |

|----------|----------------------------------------------------|----|

| Table 2. | Register Map                                       | 18 |

| Table 3. | Pin Assignment                                     | 40 |

| Table 4. | Pin Description                                    | 41 |

| Table 5. | Absolute Maximum Ratings                           | 43 |

| Table 6. | Recommended DC Operating Conditions                | 43 |

| Table 7. | LDO Characteristics                                | 43 |

| Table 8. | Power Consumption Characteristics                  | 44 |

| Table 9. | V <sub>DD</sub> Power Reset Characteristics        | 45 |

| Table 10 | . LVD/BOD Characteristics                          | 45 |

| Table 11 | . High Speed External Clock (HSE) Characteristics  | 46 |

| Table 12 | Low Speed External Clock (LSE) Characteristics     | 47 |

| Table 13 | B. High Speed Internal Clock (HSI) Characteristics | 47 |

| Table 14 | Low Speed Internal Clock (LSI) Characteristics     | 47 |

| Table 15 | . Flash Memory Characteristics                     | 48 |

| Table 16 | i. I/O Port Characteristics                        | 48 |

| Table 17 | 7. 12-Bit ADC Characteristics                      | 49 |

| Table 18 | 3. 24-Bit ADC Characteristics                      | 51 |

| Table 19 | . MCTM/GPTM/PWM Characteristics                    | 54 |

| Table 20 | ). I <sup>2</sup> C Characteristics                | 54 |

|          | . SPI Characteristics                              |    |

|          |                                                    |    |

# **List of Figures**

| Figure 1. | Block Diagram                                      | . 16 |

|-----------|----------------------------------------------------|------|

|           | Memory Map                                         |      |

|           | Clock Structure                                    |      |

|           | 24-bit A/D Converter Block Diagram                 |      |

|           | 48-pin LQFP Pin Assignment                         |      |

|           | ADC Sampling Network Model                         |      |

| -         | I <sup>2</sup> C Timing Diagrams                   |      |

|           | SPI Timing Diagrams – SPI Master Mode              |      |

|           | SPI Timing Diagrams – SPI Slave Mode with CPHA = 1 |      |

# **1** General Description

The Holtek HT32F59041 device is a high performance, low power consumption 32-bit microcontroller based around an Arm® Cortex®-M0+ processor core. The Cortex®-M0+ is a next-generation processor core which is tightly coupled with Nested Vectored Interrupt Controller (NVIC), SysTick timer, and including advanced debug support.

The device operates at a frequency of up to 20 MHz with a Flash accelerator to obtain maximum efficiency. It provides 64 KB of embedded Flash memory for code/data storage and 8 KB of embedded SRAM memory for system operation and application program usage. A variety of peripherals, such as Hardware Divider DIV, ADC, I<sup>2</sup>C, USART, UART, SPI, MCTM, GPTM, PWM, BFTM, CRC-16/32, RTC, WDT, SW-DP (Serial Wire Debug Port), etc., are also implemented in the device. Several power saving modes provide the flexibility for maximum optimization between wakeup latency and power consumption, an especially important consideration in low power applications.

The device also contains a multi-channel 24-bit Delta Sigma A/D converter which includes a programmable gain amplifier and is designed for applications that interface differentially to analog signals.

The above features ensure that the device is suitable for use in a wide range of applications, especially in areas such as white goods application controllers, power monitors, alarm systems, consumer products, handheld equipment, data logging applications, motor controllers and so on.

# **2** Features

#### Core

- 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ processor core

- Up to 20 MHz operating frequency

- Single-cycle multiplication

- Integrated Nested Vectored Interrupt Controller (NVIC)

- 24-bit SysTick timer

The Cortex®-M0+ processor is a very low gate count, highly energy efficient processor that is intended for microcontroller and deeply embedded applications that require an area optimized, low-power processor. The processor is based on the ARMv6-M architecture and supports Thumb® instruction sets, single-cycle I/O port, hardware multiplier and low latency interrupt respond time.

# **On-chip Memory**

- 64 KB on-chip Flash memory for instruction/data and options storage

- 8 KB on-chip SRAM

- Supports multiple boot modes

The Arm® Cortex®-M0+ processor accesses and debug accesses share the single external interface to external AHB peripherals. The processor accesses take priority over debug accesses. The maximum address range of the Cortex®-M0+ is 4 GB since it has a 32-bit bus address width. Additionally, a pre-defined memory map is provided by the Cortex®-M0+ processor to reduce the software complexity of repeated implementation by different device vendors. However, some regions are used by the Arm® Cortex®-M0+ system peripherals. Refer to the Arm® Cortex®-M0+ Technical Reference Manual for more information. Figure 2 in the Overview chapter shows the memory map of the device, including code, SRAM, peripheral and other pre-defined regions.

# Flash Memory Controller – FMC

- 32-bit word programming with In System Programming Interface (ISP) and In Application Programming (IAP)

- Flash protection capability to prevent illegal access

The Flash Memory Controller, FMC, provides all the necessary functions for the embedded onchip Flash Memory. The word program/page erase functions are also provided.

# Reset Control Unit - RSTCU

- Supply supervisor:

- Power on Reset / Power down Reset POR / PDR

- Brown-out Detector BOD

- Programmable Low Voltage Detector LVD

The Reset Control Unit, RSTCU, has three kinds of reset, a power on reset, a system reset and an APB unit reset. The power on reset, known as a cold reset, resets the full system during power up. A system reset resets the processor core and peripheral IP components with the exception of the SW-DP controller. The resets can be triggered by external signals, internal events and the reset generators.

# **Clock Control Unit - CKCU**

- External 4 to 20 MHz crystal oscillator

- External 32.768 kHz crystal oscillator

- Internal 20 MHz RC oscillator trimmed to ±2 % accuracy at 25 °C operating temperature

- Internal 32 kHz RC oscillator

- Independent clock divider and gating bits for peripheral clock sources

The Clock Control Unit, CKCU, provides a range of oscillator and clock functions. These include a High Speed Internal RC oscillator (HSI), a High Speed External crystal oscillator (HSE), a Low Speed Internal RC oscillator (LSI), a Low Speed External crystal oscillator (LSE), an HSE clock monitor, clock pre-scalers, clock multiplexers, APB clock divider and gating circuitry. The AHB, APB and Cortex®-M0+ clocks are derived from the system clock (CK\_SYS) which can come from the HSI, HSE, LSI or LSE. The Watchdog Timer and Real Time Clock (RTC) use either the LSI or LSE as their clock source.

# **Power Management Control Unit - PWRCU**

- Single  $V_{DD}$  power supply: 2.5 V to 5.5 V

- Integrated 1.5 V LDO regulator for CPU core, peripherals and memories power supply

- Two power domains: V<sub>DD</sub> and 1.5 V

- Three power saving modes: Sleep, Deep-Sleep1, Deep-Sleep2

Power consumption can be regarded as one of the most important issues for many embedded system applications. Accordingly the Power Control Unit, PWRCU, in the device provides many types of power saving modes such as Sleep, Deep-Sleep1 and Deep-Sleep2 mode. These operating modes reduce the power consumption and allow the application to achieve the best trade-off between the conflicting demands of CPU operating time, speed and power consumption.

## Real Time Clock - RTC

- 24-bit up-counter with a programmable prescaler

- Alarm function

- Interrupt and Wake-up event

The Real Time Clock, RTC, includes an APB interface, a 24-bit count-up counter, a control register, a prescaler, a compare register and a status register. The RTC circuits are located in the  $V_{DDI5}$  power domain. The RTC counter is used as a wakeup timer to generate a system resume or interrupt signal from the MCU power saving mode.

# **External Interrupt / Event Controller – EXTI**

- Up to 16 EXTI lines with configurable trigger source and type

- All GPIO pins can be selected as EXTI trigger source

- Source trigger type includes high level, low level, negative edge, positive edge, or both edges

- Individual interrupt enable, wakeup enable and status bits for each EXTI line

- Software interrupt trigger mode for each EXTI line

- Integrated deglitch filter for short pulse blocking

The External Interrupt/Event Controller, EXTI, comprises 16 edge detectors which can generate a wake-up event or interrupt requests independently. Each EXTI line can also be masked independently.

#### Hardware Divider - DIV

- Signed/unsigned 32-bit divider

- Operation in 8 clock cycles, load in 1 clock cycle

- Divide by zero error Flag

The divider is the truncated division and needs a software triggered start signal by using the control register "START" bit. After 8 clock cycles, the divider calculate complete flag will be set to 1, and if the divisor register data is zero, the divide by zero error flag will be set to 1.

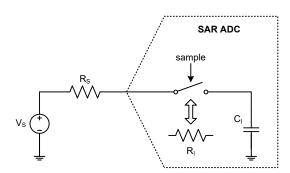

# 12-Bit Analog to Digital Converter – ADC

- 12-bit SAR ADC engine

- Up to 1 Msps conversion rate

- Up to 12 external analog input channels

A 12-bit multi-channel ADC is integrated in the device. There are multiplexed channels, which include 12 external analog signal channels and 2 internal channels which can be measured. If the input voltage is required to remain within a specific threshold window, an Analog Watchdog function will monitor and detect these signals. An interrupt will then be generated to inform the device that the input voltage is not within the preset threshold levels. There are three conversion modes to convert an analog signal to digital data. The ADC can be operated in one shot, continuous and discontinuous conversion modes.

# 24-Bit Delta Sigma Analog to Digital Converter – ΔΣ ADC

- Internal Programmable Gain Amplifier

- Internal I<sup>2</sup>C interface for external communication

- 5 Hz ~ 1.6 kHz ADC output data rate

- Internal temperature sensor for compensation

## I/O Ports - GPIO

- 30 GPIOs

- Port A, B, C are mapped as 16 external interrupts EXTI

- Almost all I/O pins have configurable output driving current

There are 30 General Purpose I/O pins, GPIO, for the implementation of logic input/output functions. Each of the GPIO ports has a series of related control and configuration registers to maximize flexibility and to meet the requirements of a wide range of applications.

The GPIO ports are pin-shared with other alternative functions to obtain maximum functional flexibility on the package pins. The GPIO pins can be used as alternative functional pins by configuring the corresponding registers regardless of the input or output pins. The external interrupts on the GPIO pins of the device have related control and configuration registers in the External Interrupt Control Unit, EXTI.

### **Basic Function Timer - BFTM**

- One 32-bit compare match count-up counter no I/O control features

- One shot mode counting stops after compare match occurs

- Repetitive mode restart counter when compare match occurs

The Basic Function Timer is a simple 32-bit up-counting counter designed to measure time intervals and generate a one shot or repetitive interrupts. The BFTM operates in two functional modes, repetitive and one shot modes. In the repetitive mode, the BFTM restarts the counter when a compare match event occurs. The BFTM also supports a one shot mode which forces the counter to stop counting when a compare match event occurs.

#### **Motor Control Timer – MCTM**

- One 16-bit up, down, up/down auto-reload counter

- 16-bit programmable prescaler allowing counter clock frequency divided by any factor between 1 and 65536

- Input Capture function

- Compare Match Output

- PWM waveform generation with Edge-aligned and Center-aligned Counting Modes

- Single Pulse Mode Output

- Complementary Outputs with programmable dead-time insertion

- Break input to force the timer's output signals into a reset or fixed condition

The Motor Control Timer consists of one 16-bit up/down-counter, four 16-bit Capture/Compare Registers (CCRs), one 16-bit Counter Reload Register (CRR), one 8-bit repetition counter and several control/status registers. It can be used for a variety of purposes including measuring the pulse width of input signals or generating output waveforms such as compare match outputs, PWM outputs or complementary PWM outputs with dead-time insertion. The MCTM is capable of offering full functional support for motor control, hall sensor interfacing and break input.

# **PWM Generation and Capture Timer – GPTM**

- One 16-bit up, down, up/down auto-reload counter

- Up to 4 independent channels for each timer

- 16-bit programmable prescaler allowing the counter clock frequency devided by any factor between 1 and 65536

- Input Capture function

- Compare Match Output

- PWM waveform generation with Edge-aligned and Center-aligned Counting Modes

- Single Pulse Mode Output

- Encoder interface controller with two inputs using quadrature decoder

The General Purpose Timer consists of one 16-bit up/down-counter, four 16-bit Capture/Compare Registers (CCRs), one 16-bit Counter Reload Register (CRR) and several control/status registers. They can be used for a variety of purposes including general time measurement, input signal pulse width measurement, output waveform generation such as single pulse generation or PWM output generation. The GPTM supports an Encoder Interface using a decoder with two inputs.

## Pulse Width Modulation – PWM

- One 16-bit up, down, up/down auto-reload counter

- Up to 4 independent channels for each timer

- 16-bit programmable prescaler allowing counter clock frequency divided by any factor between 1 and 65536

- Compare Match Output

- PWM waveform generation with Edge-aligned and Center-aligned Counting Modes

- Single Pulse Mode Output

The Pulse Width Modulator consists of one 16-bit up/down-counter, four 16-bit Compare Registers (CRs), one 16-bit Counter-Reload Register (CRR) and several control/status registers. It can be used for a variety of purposes including general timer and output waveform generation such as single pulse generation or PWM output.

# Watchdog Timer - WDT

- 12-bit down counter with 3-bit prescaler

- Reset event for the system

- Programmable watchdog timer window function

- Register write protection function

The Watchdog Timer is a hardware timing circuit that can be used to detect system failures due to software malfunctions. It includes a 12-bit count-down counter, a prescaler, a WDT delta value register, WDT operation control circuitry and a WDT protection mechanism. If the software does not reload the counter value before a Watchdog Timer underflow occurs, a reset will be generated when the counter underflows. In addition, a reset is also generated if the software reloads the counter when the counter value is greater than the WDT delta value. This means the counter must be reloaded within a limited timing window using a specific method. The Watchdog Timer counter can be stopped while the processor is in the debug mode. There is a register write protect function which can be enabled to prevent it from changing the Watchdog Timer configuration unexpectedly.

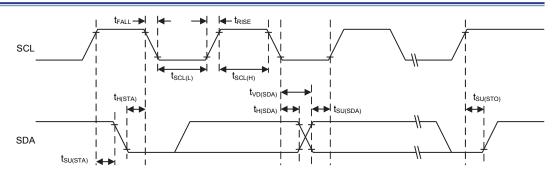

# Inter-integrated Circuit - I<sup>2</sup>C

- Supports both master and slave modes with a frequency of up to 1 MHz

- Provides an arbitration function and clock synchronization

- Supports 7-bit and 10-bit addressing modes and general call addressing

- Supports slave multi-addressing mode with address mask function

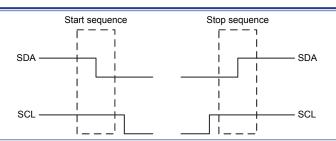

The I<sup>2</sup>C is an internal circuit allowing communication with an external I<sup>2</sup>C interface which is an industry standard two line serial interface used for connection to external hardware. These two serial lines are known as a serial data line, SDA, and a serial clock line, SCL. The I<sup>2</sup>C module provides three data transfer rates: 100 kHz in the Standard mode, 400 kHz in the Fast mode and 1 MHz in the Fast plus mode. The SCL period generation register is used to setup different kinds of duty cycle implementations for the SCL pulse.

The SDA line which is connected directly to the I<sup>2</sup>C bus is a bi-directional data line between the master and slave devices and is used for data transmission and reception. The I<sup>2</sup>C also has an arbitration detect function and clock synchronization to prevent situations where more than one master attempts to transmit data to the I<sup>2</sup>C bus at the same time.

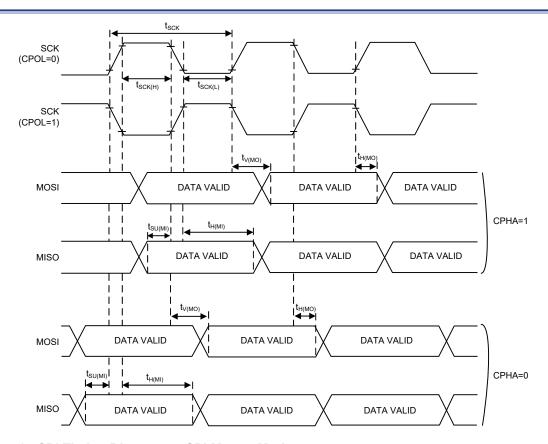

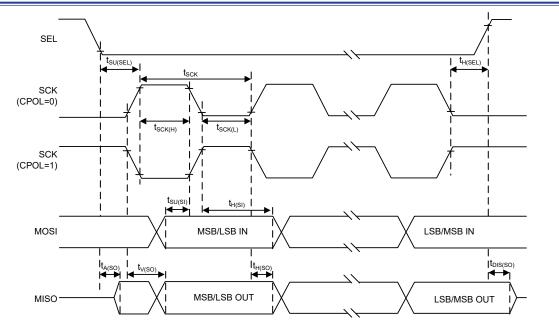

# Serial Peripheral Interface - SPI

- Supports both master and slave modes

- Frequency of up to  $(f_{PCLK}/2)$  MHz for the master mode and  $(f_{PCLK}/3)$  MHz for the slave mode

- FIFO Depth: 8 levels

- Multi-master and multi-slave operation

The Serial Peripheral Interface, SPI, provides an SPI protocol data transmit and receive function in both master and slave modes. The SPI interface uses 4 pins, which are the serial data input and output lines MISO and MOSI, the clock line, SCK, and the slave select line, SEL. One SPI device acts as a master device which controls the data flow using the SEL and SCK signals to indicate the start of data communication and the data sampling rate. To receive a data byte, the streamed data

bits are latched on a specific clock edge and stored in the data register or in the RX FIFO. Data transmission is carried out in a similar way but in a reverse sequence. The mode fault detection provides a capability for multi-master applications.

# Universal Synchronous Asynchronous Receiver Transmitter - USART

- Supports both asynchronous and clocked synchronous serial communication modes

- Asynchronous operating baud-rate clock frequency up to  $(f_{PCLK}/16)$  MHz and synchronous operating clock frequency up to  $(f_{PCLK}/8)$  MHz

- Full duplex communication

- Fully programmable serial communication characteristics including:

- Word length: 7, 8 or 9-bit character

- Parity: Even, odd or no-parity bit generation and detection

- Stop bit: 1 or 2 stop bit generation

- Bit order: LSB-first or MSB-first transfer

- Error detection: Parity, overrun and frame error

- Auto hardware flow control mode RTS, CTS

- IrDA SIR encoder and decoder

- RS485 mode with output enable control

- FIFO Depth:  $8 \times 9$  bits for both receiver and transmitter

The Universal Synchronous Asynchronous Receiver Transceiver, USART, provides a flexible full duplex data exchange using synchronous or asynchronous transfer. The USART is used to translate data between parallel and serial interfaces, and is commonly used for RS232 standard communication. The USART peripheral function supports four types of interrupt including Line Status Interrupt, Transmitter FIFO Empty Interrupt, Receiver Threshold Level Reaching Interrupt and Time Out Interrupt. The USART module includes a transmitter FIFO (TX FIFO) and receiver FIFO (RX FIFO). The software can detect a USART error status by reading the Line Status Register, LSR. The status includes the type and the condition of transfer operations as well as several error conditions resulting from Parity, Overrun, Framing and Break events.

# **Universal Asynchronous Receiver Transmitter – UART**

- Asynchronous serial communication operating baud-rate clock frequency up to (f<sub>PCLK</sub>/16) MHz

- Full duplex communication

- Fully programmable serial communication characteristics including:

- Word length: 7, 8 or 9-bit character

- Parity: Even, odd or no-parity bit generation and detection

- Stop bit: 1 or 2 stop bit generation

- Bit order: LSB-first or MSB-first transfer

- Error detection: Parity, overrun and frame error

The Universal Asynchronous Receiver Transceiver, UART, provides a flexible full duplex data exchange using asynchronous transfer. The UART is used to translate data between parallel and serial interfaces, and is commonly used for RS232 standard communication. The UART peripheral function supports Line Status Interrupt. The software can detect a UART error status by reading

the Line Status Register, LSR. The status includes the type and the condition of transfer operations as well as several error conditions resulting from Parity, Overrun, Framing and Break events.

# Cyclic Redundancy Check - CRC

- Support CRC16 polynomial: 0x8005,  $X^{16} + X^{15} + X^2 + 1$

- Support CCITT CRC16 polynomial: 0x1021,  $X^{16} + X^{12} + X^5 + 1$

- Support IEEE-802.3 CRC32 polynomial: 0x04C11DB7,  $X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^{8} + X^{7} + X^{5} + X^{4} + X^{2} + X + 1$

- Supports 1's complement, byte reverse & bit reverse operation on data and checksum

- Supports byte, half-word & word data size

- Programmable CRC initial seed value

- CRC computation executed in 1 AHB clock cycle for 8-bit data and 4 AHB clock cycles for 32-bit data

The CRC calculation unit is an error detection technique test algorithm which is used to verify data transmission or storage data correctness. A CRC calculation takes a data stream or a block of data as its input and generates a 16-bit or 32-bit output remainder. Ordinarily, a data stream is suffixed by a CRC code and used as a checksum when being sent or stored. Therefore, the received or restored data stream is calculated by the same generator polynomial as described above. If the new CRC code result does not match the one calculated earlier, that means the data stream contains a data error.

# **Debug Support**

- Serial Wire Debug Port SW-DP

- 4 comparators for hardware breakpoint or code / literal patch

- 2 comparators for hardware watch points

# **Package and Operation Temperature**

- 48-pin LQFP package

- Operation temperature range: -40 °C to +85 °C

# **3** Overview

# **Device Information**

**Table 1. Features and Peripheral List**

| Per                    | ipherals         | HT32F59041     |  |  |

|------------------------|------------------|----------------|--|--|

| Main Flash (KB)        |                  | 63             |  |  |

| Option Bytes Flash (Ki | 3)               | 1              |  |  |

| SRAM (KB)              |                  | 8              |  |  |

|                        | MCTM             | 1              |  |  |

|                        | GPTM             | 1              |  |  |

| Timoro                 | PWM              | 2              |  |  |

| Timers                 | BFTM             | 2              |  |  |

|                        | WDT              | 1              |  |  |

|                        | RTC              | 1              |  |  |

| Communication          | SPI              | 2              |  |  |

|                        | USART            | 1              |  |  |

|                        | UART             | 2              |  |  |

|                        | I <sup>2</sup> C | 2              |  |  |

| Hardware Divider       |                  | 1              |  |  |

| CRC-16/32              |                  | 1              |  |  |

| EXTI                   |                  | 16             |  |  |

| 12-bit ADC             |                  | 1              |  |  |

| Number of channels     |                  | 12 Channels    |  |  |

| 24-bit ADC             |                  | 1              |  |  |

| Number of channels     |                  | 4 Channels     |  |  |

| GPIO                   |                  | 30             |  |  |

| CPU frequency          |                  | Up to 20 MHz   |  |  |

| Operating voltage      |                  | 2.5 V ~ 5.5 V  |  |  |

| Operating temperature  | ;                | -40 °C ~ 85 °C |  |  |

| Package                |                  | 48-pin LQFP    |  |  |

Note: The detailed functions listed here, except the 24-bit Delta Sigma A/D Converter, are compatible with the HT32F50241 device. Refer to the HT32F50241 user manual for detailed function descriptions.

# **Block Diagram**

Figure 1. Block Diagram

# **Memory Map**

Figure 2. Memory Map

Table 2. Register Map

| Start Address         End Address         Peripheral         Bus           0x4000_0000         0x4000_0FFF         USART           0x4000_1000         0x4000_1FFF         UARTO           0x4000_4000         0x4000_3FFF         Reserved           0x4000_5000         0x4000_4FFF         SPI0           0x4001_0000         0x4001_0FFF         ADC           0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_3FF         Reserved           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_3FFF         Reserved           0x4002_5000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_5FFF         Reserved           0x4002_0000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_1FFF         UART1           0x4004_4000         0x4004_1FFF         UART1           0x4004_4000         0x4004_1FFF         Reserved           0x4004_8000         0x4004_1FFF         Reserved           0x4004_8000         0x4004_1FFF         Reserved <th>01 11 11</th> <th colspan="2"></th> <th>_</th>                 | 01 11 11      |             |                   | _   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------------|-----|

| 0x4000_1000         0x4000_1FFF         UARTO           0x4000_2000         0x4000_3FFF         Reserved           0x4000_4000         0x4000_4FFF         SPI0           0x4000_5000         0x4000_FFFF         Reserved           0x4001_0000         0x4001_0FFF         ADC           0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_0000         0x4002_CFFF         MCTM           0x4002_0000         0x4003_1FFF         PWM0           0x4003_1000         0x4003_1FFF         PWM0           0x4004_1000         0x4004_1FFF         Reserved           0x4004_1000         0x4004_1FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_4000         0x4004_4FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C1           0x4004_8000         0x4004_8FF         I²C1           0x4006_8000         0x4006_8FFF         WDT           0x4006_8000 </th <th>Start Address</th> <th>End Address</th> <th>Peripheral</th> <th>Bus</th> | Start Address | End Address | Peripheral        | Bus |

| 0x4000_2000         0x4000_3FFF         Reserved           0x4000_4000         0x4000_4FFF         SPI0           0x4000_5000         0x4000_FFFF         Reserved           0x4001_0000         0x4001_0FFF         ADC           0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FF         EXTI           0x4002_5000         0x4002_4FF         Reserved           0x4002_5000         0x4003_0FFF         Reserved           0x4002_0000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_8000         0x4004_8FFF         I°C0           0x4004_8000         0x4004_8FFF         I°C1           0x4006_8000         0x4006_8FF         WDT           0x4006_8000         0x4006_8FF         Reserved           0x4006_80                                                                                 | <del>_</del>  | _           | USART             |     |

| 0x4000_4000         0x4000_4FFF         SPI0           0x4000_5000         0x4000_FFFF         Reserved           0x4001_0000         0x4001_0FFF         ADC           0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_0000         0x4002_CFFF         MCTM           0x4002_0000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_2000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_4FFF         Reserved           0x4004_8000         0x4004_4FFF         Reserved           0x4004_9000         0x4006_8FF         WDT           0x4006_8000         0x4006_8FF         WDT           0x4006_9000         0x4006_9FF         Reserved           0x4006_B                                                                                 | 0x4000_1000   | 0x4000_1FFF | UART0             |     |

| 0x4000_5000         0x4000_FFFF         Reserved           0x4001_0000         0x4001_0FFF         ADC           0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_5000         0x4002_FFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_3FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_4FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_9000         0x4004_9FFF         I²C1           0x4006_8000         0x4006_9FF         Reserved           0x4006_9000         0x4006_9FF         Reserved           0x4006_B000         0x4006_BFF         Reserved           0x4006_                                                                                 | 0x4000_2000   | 0x4000_3FFF | Reserved          |     |

| 0x4001_0000         0x4001_0FFF         ADC           0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_8FFF         I²C0           0x4004_8000         0x4004_8FFF         I²C1           0x4004_9000         0x4004_8FFF         Reserved           0x4004_A000         0x4006_8FF         WDT           0x4006_8000         0x4006_8FF         REServed           0x4006_B000         0x4006_FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_B                                                                                 | 0x4000_4000   | 0x4000_4FFF | SPI0              |     |

| 0x4001_1000         0x4002_1FFF         Reserved           0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_8FFF         I²C0           0x4004_8000         0x4004_8FFF         I²C1           0x4004_9000         0x4004_9FFF         Reserved           0x4004_A000         0x4006_8FF         WDT           0x4006_8000         0x4006_8FF         RC2           0x4006_B000         0x4006_FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_F0                                                                                 | 0x4000_5000   | 0x4000_FFFF | Reserved          |     |

| 0x4002_2000         0x4002_2FFF         AFIO           0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_8FFF         I²C0           0x4004_8000         0x4004_8FFF         I²C1           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_8FF         WDT           0x4006_8000         0x4006_8FF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_F000         0x4007_FFF         Reserved           0x4007_1                                                                                 | 0x4001_0000   | 0x4001_0FFF | ADC               |     |

| 0x4002_3000         0x4002_3FFF         Reserved           0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_3FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FF         Reserved           0x4006_8000         0x4006_8FF         WDT           0x4006_9000         0x4006_9FF         Reserved           0x4006_B000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_FFF         GPTM           0x4006_F000         0x4006_FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x400                                                                                 | 0x4001_1000   | 0x4002_1FFF | Reserved          |     |

| 0x4002_4000         0x4002_4FFF         EXTI           0x4002_5000         0x4002_BFFF         Reserved           0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4004_0FFF         PWM0           0x4004_2000         0x4004_0FFF         Reserved           0x4004_2000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_B000         0x4006_FFF         Reserved           0x4006_F000         0x4006_FFF         Reserved           0x4006_F000         0x4007_FFF         Reserved           0x4007_1000         0x4007_FFF         Reserved           0x                                                                                 | 0x4002_2000   | 0x4002_2FFF | AFIO              |     |

| 0x4002_5000         0x4002_BFFF         Reserved           0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_8FFF         I²C0           0x4004_8000         0x4004_9FFF         I²C1           0x4004_9000         0x4004_9FFF         Reserved           0x4004_A000         0x4006_8FF         WDT           0x4006_8000         0x4006_8FF         WDT           0x4006_9000         0x4006_9FF         Reserved           0x4006_B000         0x4006_AFFF         RC & PWRCU           0x4006_B000         0x4006_BFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_7FFF         BFTM0           0x4007_70                                                                                 | 0x4002_3000   | 0x4002_3FFF | Reserved          |     |

| 0x4002_C000         0x4002_CFFF         MCTM           0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_B000         0x4006_PFF         Reserved           0x4006_B000         0x4006_PFF         Reserved           0x4006_F000         0x4006_FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                           | 0x4002_4000   | 0x4002_4FFF | EXTI              |     |

| 0x4002_D000         0x4003_0FFF         Reserved           0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_8000         0x4006_8FFF         RTC & PWRCU           0x4006_8000         0x4006_AFFF         Reserved           0x4006_B000         0x4006_DFFF         Reserved           0x4006_B000         0x4006_FFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                   | 0x4002_5000   | 0x4002_BFFF | Reserved          |     |

| 0x4003_1000         0x4003_1FFF         PWM0           0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_FFF         RC & PWRCU           0x4006_B000         0x4006_FFF         GPTM           0x4006_F000         0x4006_FFF         Reserved           0x4006_F000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                    | 0x4002_C000   | 0x4002_CFFF | MCTM              |     |

| 0x4003_2000         0x4004_0FFF         Reserved           0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_B000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                       | 0x4002_D000   | 0x4003_0FFF | Reserved          |     |

| 0x4004_1000         0x4004_1FFF         UART1           0x4004_2000         0x4004_3FFF         Reserved           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_BFFF         GPTM           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                      | 0x4003_1000   | 0x4003_1FFF | PWM0              |     |

| 0x4004_2000         0x4004_3FFF         Reserved         APB           0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                               | 0x4003_2000   | 0x4004_0FFF | Reserved          |     |

| 0x4004_4000         0x4004_4FFF         SPI1           0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x4004_1000   | 0x4004_1FFF | UART1             |     |

| 0x4004_5000         0x4004_7FFF         Reserved           0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_7FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x4004_2000   | 0x4004_3FFF | Reserved          | APB |

| 0x4004_8000         0x4004_8FFF         I²C0           0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x4004_4000   | 0x4004_4FFF | SPI1              |     |

| 0x4004_9000         0x4004_9FFF         I²C1           0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x4004_5000   | 0x4004_7FFF | Reserved          |     |

| 0x4004_A000         0x4006_7FFF         Reserved           0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x4004_8000   | 0x4004_8FFF | I <sup>2</sup> C0 |     |

| 0x4006_8000         0x4006_8FFF         WDT           0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x4004_9000   | 0x4004_9FFF | I <sup>2</sup> C1 |     |

| 0x4006_9000         0x4006_9FFF         Reserved           0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x4004_A000   | 0x4006_7FFF | Reserved          |     |

| 0x4006_A000         0x4006_AFFF         RTC & PWRCU           0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x4006_8000   | 0x4006_8FFF | WDT               |     |

| 0x4006_B000         0x4006_DFFF         Reserved           0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x4006_9000   | 0x4006_9FFF | Reserved          |     |

| 0x4006_E000         0x4006_EFFF         GPTM           0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x4006_A000   | 0x4006_AFFF | RTC & PWRCU       |     |

| 0x4006_F000         0x4007_0FFF         Reserved           0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0x4006_B000   | 0x4006_DFFF | Reserved          |     |

| 0x4007_1000         0x4007_1FFF         PWM1           0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0x4006_E000   | 0x4006_EFFF | GPTM              |     |

| 0x4007_2000         0x4007_5FFF         Reserved           0x4007_6000         0x4007_6FFF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x4006_F000   | 0x4007_0FFF | Reserved          |     |

| 0x4007_6000         0x4007_6FF         BFTM0           0x4007_7000         0x4007_7FFF         BFTM1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x4007_1000   | 0x4007_1FFF | PWM1              |     |

| 0x4007_7000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x4007_2000   | 0x4007_5FFF | Reserved          |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x4007_6000   | 0x4007_6FFF | BFTM0             |     |

| 0x4007_8000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x4007_7000   | 0x4007_7FFF | BFTM1             |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x4007_8000   | 0x4007_FFFF | Reserved          |     |

| Start Address | End Address | Peripheral | Bus |

|---------------|-------------|------------|-----|

| 0x4008_0000   | 0x4008_1FFF | FMC        |     |

| 0x4008_2000   | 0x4008_7FFF | Reserved   |     |

| 0x4008_8000   | 0x4008_9FFF | CKCU/RSTCU |     |

| 0x4008_A000   | 0x4008_BFFF | CRC        |     |

| 0x4008_C000   | 0x400A_FFFF | Reserved   |     |

| 0x400B_0000   | 0x400B_1FFF | GPIOA      | AHB |

| 0x400B_2000   | 0x400B_3FFF | GPIOB      |     |

| 0x400B_4000   | 0x400B_5FFF | GPIOC      |     |

| 0x400B_6000   | 0x400C_9FFF | Reserved   |     |

| 0x400C_A000   | 0x400C_BFFF | DIV        |     |

| 0x400C_C000   | 0x400F_FFFF | Reserved   |     |

# **Clock Structure**

Figure 3. Clock Structure

# 4

# 24-Bit Delta Sigma A/D Converter – ΔΣ ADC

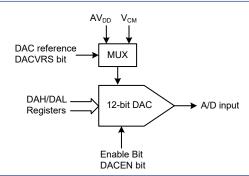

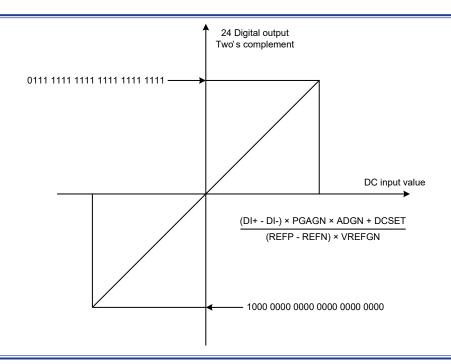

The device contains a high accuracy multi-channel 24-bit Delta Sigma type analog-to-digital converter which can directly interface to external analog signals, such as that from sensors or other control signals and convert these signals directly into a 24-bit digital value. In addition to the core analog to digital converter circuitry, the A/D converter module also includes an internal Programmable Gain Amplifier PGA. The PGA gain control, ADC gain control and ADC reference gain control determine the overall amplification gain for ADC input signal, giving users a flexible way of setting up an overall gain to achieve an optimum amplification of the input signal for their specific applications. The converter has a total of four inputs allowing the formation of two differential input channels. The converter output is filtered via a SINC filter and the result stored as a 24-bit value in three data registers. An internal voltage regulator and reference sources are also included as well as a temperature sensor for A/D converter compensation due to temperature effects.

Figure 4. 24-bit A/D Converter Block Diagram

# 24-Bit A/D Converter Internal Registers

The 24-bit A/D converter is setup and operated using a series of internal registers. Device commands and data are written to and read from the 24-bit ADC module using its internal I<sup>2</sup>C bus. This list provides a summary of all the 24-bit ADC module internal registers, their detailed operation is described under their relevant section in the functional description.

# **Register Initial Values**

The following table shows the internal value of the individual register after a power on reset.

| Register | Power On Reset Value |  |  |

|----------|----------------------|--|--|

| PWRC     | 0000 0000            |  |  |

| PGAC0    | -000 0000            |  |  |

| PGAC1    | -000 000-            |  |  |